#### **PROPRIETARY NOTICE**

All rights reserved by Janz Tec AG.

No parts of this technical manual may be modified, copied or reproduced in any form or by any means for commercial use without the prior written permission of Janz Tec AG, Germany.

All instructions, information and specification contained in this manual are for reference only and remain subject to change without announcement.

# emPC-CXR

rugged embedded PC

(Hardware Manual)

Version V1.4

refers to product revision no. V1.0

Title:rugged embedded PCFile:j:\as\entwicklung\projekte\hw\empc\empc\_cxr\doc\manual\_empc-cxr\_hardware.docPattern:\\ntserv5\janzgrp\as\entwicklung\formulare\entwicklung (ew)\ew\_manual.dotCreated:Stefan Althöfer, 21.05.2014Last Update:Stefan Althöfer, 14.11.2018

© Janz Tec AG 2015

Im Dörener Feld 8 D-33100 Paderborn, Germany

Tel.:

+49-5251-1550-0

FAX:

+49-5251-1550-190

email:

support@janztec.com

Internet:

www.janztec.com

# Contents

| 1 | Introd                       | uction                                                  | 5       |

|---|------------------------------|---------------------------------------------------------|---------|

|   | 1.1<br>1.1.1<br>1.1.2<br>1.2 | Features<br>Hardware<br>Software<br>Functional Overview | 5<br>5  |

| 2 |                              | Instructions                                            | 7       |

|   | 2.1                          | Installation and Maintenance                            |         |

| 3 | 2.2<br>Install               | Ambient and Environmental Conditions                    | 88<br>9 |

| 3 |                              |                                                         | -       |

|   | 3.1                          | Mounting                                                |         |

|   | 3.1.1                        | Mounting Screws                                         |         |

|   | 3.1.2                        | Mounting Wall                                           |         |

|   | 3.2                          | Connectors and Operators                                |         |

|   | 3.2.1                        | POWER IN                                                |         |

|   | 3.2.2                        | VGA connector                                           |         |

|   | 3.2.3                        | Ethernet Interfaces LAN1 and LAN2                       |         |

|   | 3.2.4                        | USB 2.0 Host Interfaces USB1 and USB2                   |         |

|   | 3.2.5                        | CAN                                                     |         |

|   | 3.2.6                        | R\$485                                                  |         |

|   | 3.2.7                        | RS232                                                   |         |

|   | 3.2.8                        | Digital IO                                              |         |

|   | 3.3                          | Application Hints                                       |         |

|   | 3.3.1                        | Right Angle Cable                                       |         |

|   | 3.3.2                        | M12 Y Adapters                                          | 16      |

| 4 | Mainte                       | enance                                                  | 17      |

|   | 4.1                          | Handling Top Cover                                      | 18      |

|   | 4.2                          | Battery Replacement                                     | 19      |

|   | 4.3                          | mSATA                                                   | 19      |

| 5 | Hardw                        | vare details                                            | 21      |

|   | 5.1                          | PCI Express                                             | 21      |

|   | 5.2                          | Ethernet                                                |         |

|   | 5.2.1                        | LAN1                                                    |         |

|   | 5.2.1                        | LAN2                                                    |         |

| • | -                            |                                                         |         |

| 6 | FPGA                         | expansion subsystem                                     | 22      |

|   | 6.1                          | Control Registers                                       |         |

|   | 6.1.1                        | Feature detection                                       |         |

|   | 6.1.2                        | Interrupt programming                                   |         |

|   | 6.1.3                        | Function Reset                                          |         |

|   | 6.1.4                        | Internal I <sup>2</sup> C bus                           |         |

|   | 6.2                          | CAN Interface                                           |         |

|   | 6.2.1                        | CAN address space                                       |         |

|   | 6.2.2                        | CAN termination and LEDs                                |         |

|   | 6.3                          | Serial Port Interface                                   |         |

|   | 6.3.1                        | Serial Port address space                               |         |

|   | 6.4                          | NVRAM                                                   |         |

|   | 6.5                          | Digital IO                                              |         |

|   | 6.6                          | FPGA Reprogramming                                      | 29      |

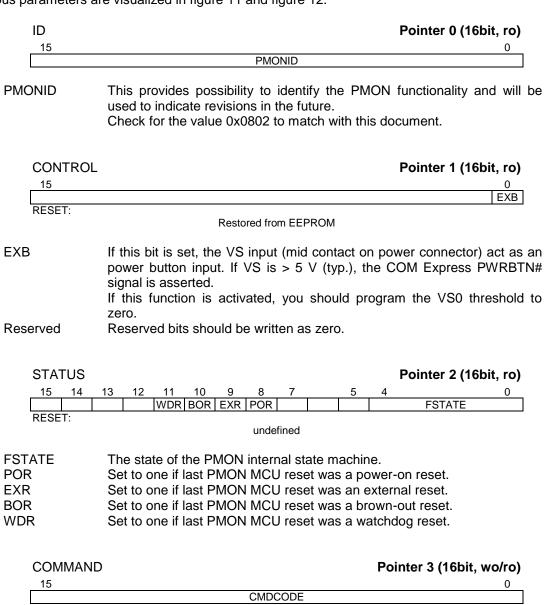

| 7 | Syste | em Control            | 30 |

|---|-------|-----------------------|----|

|   | 7.1.1 | I2C Address           |    |

|   | 7.1.2 | I2C Registers         |    |

|   | 7.1.3 | Command Codes         |    |

| 8 | Appe  | ndices                | 38 |

|   | 8.1   | Technical Data        |    |

|   | 8.2   | References            |    |

|   | 8.3   | M12 Connector Ratings | 41 |

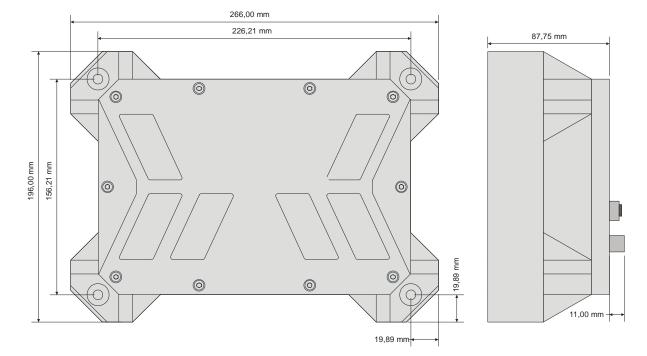

|   | 8.4   | Dimensions            |    |

|   | 8.5   | Product History       | 43 |

|   | 8.6   | Manual History        |    |

|   |       | -                     |    |

# **List of Figures**

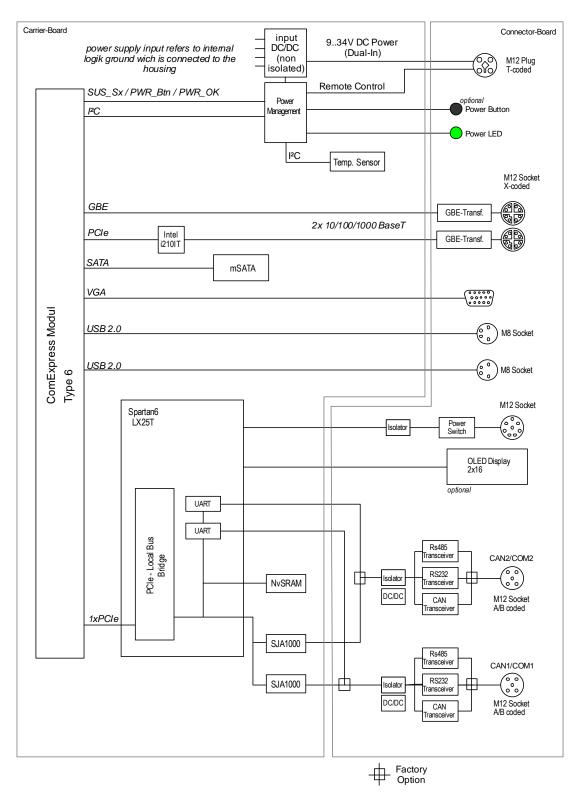

| figure 1: block diagram                                 | 6  |

|---------------------------------------------------------|----|

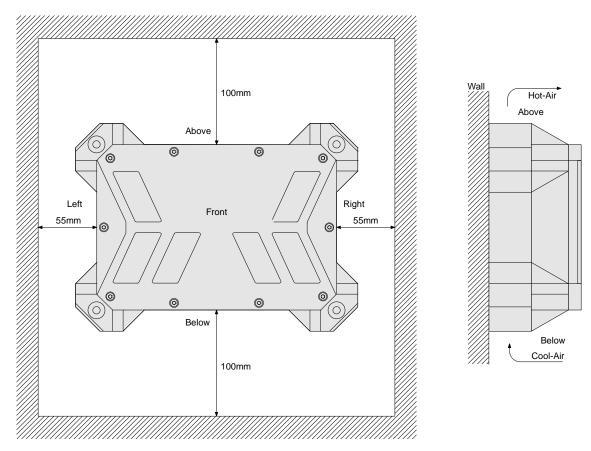

| figure 2: Mounting guidelines                           | 9  |

| figure 3: front view with connectors                    | 11 |

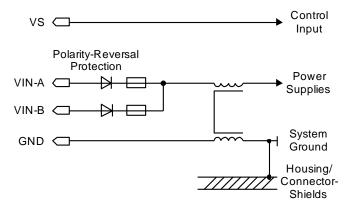

| figure 4: Power Supply Input                            | 12 |

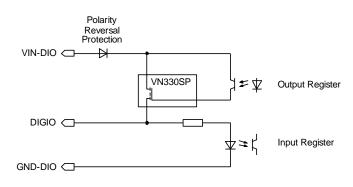

| figure 5: DIO structure                                 |    |

| figure 6: right angle cable example                     |    |

| figure 7: M12 Y-connectors                              | 16 |

| figure 8: Handling the Top Cover                        | 18 |

| figure 9: Removing and replacing coin cell battery      | 19 |

| Figure 10: emPC-CXR system supervision                  |    |

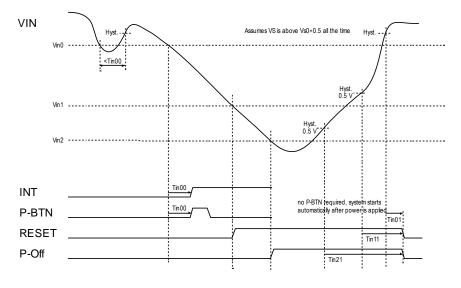

| figure 11: System control by power supply voltage (VIN) |    |

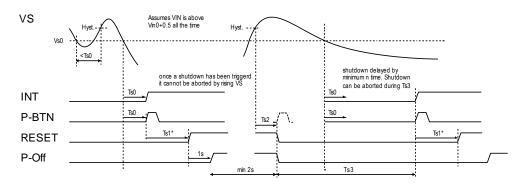

| figure 12:System control by remote control input (VS)   |    |

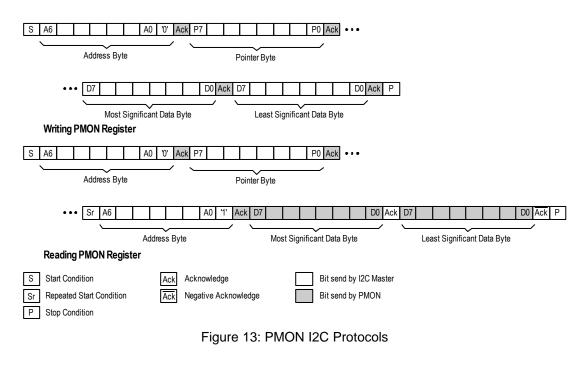

| Figure 13: PMON I2C Protocols                           |    |

| figure 14: housing dimensions                           |    |

# List of Tables

| table 1: Power supply connector                     | 12 |

|-----------------------------------------------------|----|

| table 2: VGA connector                              | 13 |

| table 3: Ethernet connector                         | 13 |

| table 4: USB connector with USB cables colour codes |    |

| table 5: M12 CAN connector                          | 13 |

| table 6: M12 RS485 connector                        | 14 |

| table 7: M12 RS232 connector                        |    |

| table 8: M12 RS232 connector                        | 14 |

| Table 9: COM Express PCIe lane usage                | 21 |

| Table 10: PCI identification                        |    |

| Table 11: Local address spaces                      | 22 |

| Table 12: Control registers                         | 23 |

| Table 13: NVRAM address (128KByte NVRAM)            |    |

| Table 14: Digital IO registers                      | 28 |

|                                                     |    |

# About this Manual

This is the hardware manual for the emPC-CXR rugged embedded PC.

# Conventions

If numbers are specified in this manual, they will be either decimal or hexadecimal. We use C-notation to identify hexadecimal numbers (the 0x prefix).

If we refer to low active signal names, they will suffixed by a "#" character.

Some parts of the contains notices you have to observe to ensure your personal safety, or to prevent damage to property. These are visually marked with the following alert symbols:

Indicates that death or severe personal injury *will* result if proper precautions are not taken.

# WARNING

DANGER

Indicates that death or severe personal injury *may* result if proper precautions are not taken.

| / | ſ |          |  |

|---|---|----------|--|

|   | ۰ | <b>\</b> |  |

### CAUTION

Indicates that *minor* personal injury can result if proper precautions are not taken.

### NOTICE

Indicates that damage to equipment can result if proper precautions are not taken.

Indicates information that we think you should have read to save your time by avoiding common problems. Important suggestions that should be followed will also be marked with this sign.

### Acronyms and Abbreviations

- EMC Electromagnetic capability.

- ESD Electrostatic discharge.

- GND System ground potential. Inside the product this is connected to the metal housing, which might be connected to protective earth by the installation. There exist some isolated reference grounds for communication interfaces or IO. These reference signals are referred to as GND-x, where x indicates function.

# 1 Introduction

### 1.1 Features

### 1.1.1 Hardware

- COM Express Processing Core

- Intel Core i7-3517UE

- o Intel Celeron 1047UE

- DDR3 memory as defined by COM Express Module

- Internal mSATA socket for SATA based SSD modules

- 2 x 10/100/1000 Mbit/s Ethernet on M12 connector

- 2 x USB interface on M8 connector

- 128 kB of nvSRAM (which does not require battery backup)

- Battery backed up RTC

- COM express internal watchdog function

- Power supply/temperature monitoring

- VGA display connector D-SUB

- Two 5 pin M12 connectors for serial ports. Customizable as:

- CAN (isolated)

- RS232/RS485 (isolated)

- 4 digital IO (in/out) on M12 connector (isolated, externally powered)

- System Power supply 9..34 VDC on M12 connector

- Power LED

- Optional 2x16 character display and user defined buttons

### 1.1.2 Software

Supported by

- Windows 7

- Windows 7 embedded

- Linux

Contact Janz Tec for more information about the available software packages.

### **1.2 Functional Overview**

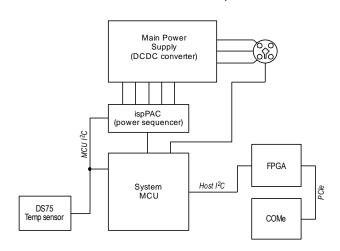

The functional components of the product are shown in figure 1.

figure 1: block diagram

# 2 Safety Instructions

Refer to page iv for explanation of the warning notice system.

The product described in this documentation may be operated only by personnel qualified for the specific task in accordance with the relevant documentation for the specific task, in particular its warning notices and safety instructions. Qualified personnel are those who, based on their training and experience, are capable of identifying risks and avoiding potential hazards when working with these products.

### 2.1 Installation and Maintenance

The power supply of the product operates with hazardous voltages.

### **DANGER: Electrical Shock**

Danger to life.

This product operates with 9..34 V DC SELV power supply. Do *not* connect this product to an improper power supply (No AC power, no more than 34 V DC or no non-SELV circuit)!

#### DANGER: Electrical Shock Danger to life.

The IO interfaces (connectors) of the product are only suited to be connected to SELV circuits. Use interfaces (connectors) for their intended use only. This product must not be connected to telecommunication networks (TNV circuits).

### **CAUTION: Explosive Risk**

The installed computer board is equipped with a Lithium battery. Danger of explosion if battery is incorrectly replaced. Replace only with battery of the same or equivalent type.

### CAUTION: Fire Risk

The digital IO must be powered by a SELV power supply, that complies with the requirements of a limited energy source (LPS) (By using an appropriate supply or an external fuse).

#### WARNING: Burns Hazard

The product generates considerable amount of heat. The housing transports this heat to the environment and therefore gets hot. **Caution when touching the housing, burns hazard**!

To comply with UL/IEC/EN 60950-1: If the product is not supplied by a limited current circuit, then a disconnection means - easily accessible and identifiable - has to be provided in the final installation to separate the equipment from all power sources.

# 2.2 Ambient and Environmental Conditions

#### **CAUTION:** Damage

Do not operate the product beyond the specified ambient conditions

### DANGER: Explosive Risk

Do not operate the product in potentially explosive atmosphere..

### NOTICE: EMI

This product is a class A device. This product may cause radio interference. In this case the user must take adequate measures.

### NOTICE

UL Applications: For outdoor use, the product has to be mounted in a suitable electrical enclosure complying with enclosure requirement of UL50, UL50E and the max. supply voltage shall be 30VDC in normal and single fault condition to comply with voltage requirements of UL60950-2-22.

# 3 Installation

### CAUTION

The product is designed as a fan less computer system. Nevertheless a certain amount of heat is generated inside the housing. The housing transports this heat to the environment. **Caution when touching the housing, burns hazard**!

The product can be operated with DC power supply from 9 to 34 V.

# 3.1 Mounting

The emPC-CXR is intended to be mounted on a flat surface wall.

figure 2: Mounting guidelines

NOTICE The product must be mounted exactly as indicated in figure 2 to allow the required natural heat transfer. Derivations of < 5 ° do not matter. The indicated area must be free of obstacles which prevent heat transfer. There should be no space between the wall and the product (use no spacers for mounting).

### NOTICE

The ambient temperatures **below**, **left**, **right** and in **front** of the product must not exceed the specified maximum ambient temperature.

### 3.1.1 Mounting Screws

The product must be mounted with M6 Screws with appropriate washers. Stainless steel is recommended in harsh environment. The washers may have a maximum diameter of 15 mm.

#### 3.1.2 Mounting Wall

### NOTICE

The mounting wall must have enough structural integrity at high temperatures. The Case temperature of the product will be approximately 15 K higher than the ambient temperature.

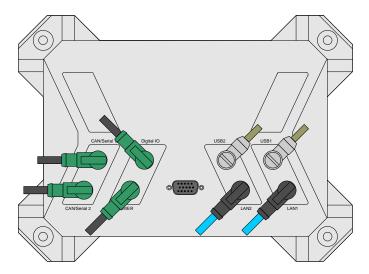

### $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ USB1 USB2 CAN/Serial 1 Digital IO CAN/Serial 2 POWER LAN2 LAN1 $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ Ο

## 3.2 Connectors and Operators

figure 3: front view with connectors

Below the VGA connector you find an M5 thread for an additional earth connection. EMI Tests were passed without extra earth connection. However, during EMI testing, earth connection was established with the shields of the IO cables (VGA, LAN, ...).

The green power LED between the USB connectors lights when the system is running. It does not light when the system is in power down mode even if power is applied at the power connector.

| Ń | <b>NOTICE</b><br>Do not actuate connectors when power is applied.                                                                             |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                               |

| Ŵ | <b>NOTICE</b><br>All connectors (M12/M8/DSUB) are not sealed when no mating connector is present. Use a screw plug to seal unused connectors. |

| Â | <b>NOTICE</b><br>Mechanical actuation of M12/M8 connectors is prohibited below -25 °C.                                                        |

### 3.2.1 POWER IN

The system power supply is connected with a 4 pin T-coded M12 male connector.

| 4 pin | male | M12 | T-coded |

|-------|------|-----|---------|

|-------|------|-----|---------|

| 1 | VIN-A | (934V DC) |

|---|-------|-----------|

| 2 | VIN-B | (934V DC) |

| 3 | VS    |           |

| 4 | GND   |           |

table 1: Power supply connector

## DANGER

The product may only be operated with power supplies which can be considered SELV circuits.

The return of the power supply (pin 4 = GND) is connected to the internal system GND (via EMI filter chokes). The internal system GND is connected to the housing internally. Hence the shells of all connectors are on system GND potential.

figure 4: Power Supply Input

To comply with UL/IEC/EN 60950-1 : If the product is not supplied by a limited current circuit, then a disconnection means - easily accessible and identifiable - has to be provided in the final installation to separate the equipment from all power sources.

The specified power supply voltage range is defined at the input connector of the product. At low input voltage and high system load, a high input current of several ampere will flow. This can lead to substantial drop on the power input cable (even when using 1.5 mm<sup>2</sup> M12 cable assemblies).

#### 3.2.2 VGA connector

Analog VGA graphics connector as supplied by the COMexpress module.

| 1 | Red   | 9  | +5V       |

|---|-------|----|-----------|

| 2 | Green | 10 | GND       |

| 3 | Blue  | 11 | N/C       |

| 4 | N/C   | 12 | DDC Data  |

| 5 | GND   | 13 | HSync     |

| 6 | GND   | 14 | VSync     |

| 7 | GND   | 15 | DDC Clock |

| 8 | GND   |    |           |

table 2: VGA connector

#### 3.2.3 Ethernet Interfaces LAN1 and LAN2

Ethernet interfaces of the motherboard. The Ethernet physics is 10/100/1000BaseT, available through the shielded M12 connectors.

8 pin female M12 X-coded

| 1 | MDI0+ | 5 | MDI3+ |

|---|-------|---|-------|

| 2 | MDI0- | 6 | MDI3- |

| 3 | MDI1+ | 7 | MDI2+ |

| 4 | MDI1- | 8 | MDI2- |

table 3: Ethernet connector

#### 3.2.4 USB 2.0 Host Interfaces USB1 and USB2

2 USB 2.0 host interfaces are available through 4 pin M8 female connectors.

4 pin M8

| 1 | +5V (red)    |

|---|--------------|

| 2 | USB- (white) |

| 3 | GND (black)  |

| 4 | USB+ (green) |

table 4: USB connector with USB cables colour codes

The USB connectors do not provide standby power, thus wake on USB is not possible.

### 3.2.5 CAN

If the product is equipped with CAN interface(s), 5 pin A-coded M12 female connectors are equipped for the CAN.

| 1 | NC      |

|---|---------|

| 2 | NC      |

| 3 | GND-CAN |

| 4 | CAN-H   |

| 5 | CAN-L   |

table 5: M12 CAN connector

#### 3.2.6 RS485

If the product is equipped with RS485 interface(s), 5 pin B-coded M12 female connectors are equipped.

| 5 pin female M12 B-coded |

|--------------------------|

| 1 | NC        |

|---|-----------|

| 2 | DM (A)    |

| 3 | GND-RS485 |

| 4 | DP (B)    |

| 5 | NC        |

table 6: M12 RS485 connector

#### 3.2.7 RS232

If the product is equipped with RS232 interface(s), 5 pin B-coded M12 female connectors are equipped.

5 pin female M12 B-coded

| 1 | RTS (out) |

|---|-----------|

| 2 | TxD (out) |

| 3 | GND-RS232 |

| 4 | RxD (in)  |

| 5 | CTS (in)  |

table 7: M12 RS232 connector

### 3.2.8 Digital IO

4 digital IO signals are available on 8 pin A-M12 female connector.

| 1 | VIN-DIO (1034V DC) |

|---|--------------------|

| 2 | DIO4               |

| 3 | DIO3               |

| 4 | DIO2               |

| 5 | DIO1               |

| 6 | NC                 |

| 7 | NC                 |

| 8 | GND-DIO            |

table 8: M12 RS232 connector

### CAUTION

The digital IO must be powered by a SELV power supply, that complies with the requirements of a limited energy source (LPS) (By using an appropriate supply or an external fuse).

Digital IO pins drive VIN-DIO to the output pins (high side switch). Each digital IO pins can be read back so that it can be used as input as well. See figure 5 for details.

figure 5: DIO structure

Each port pin (DIO1...DIO4) is able to source 500mA into a load. The sum of all output currents should be limited to 1A.

### NOTICE

When outputs are turned on, they source power from VIN-DIO to the output pin. If you use a pin as input, make sure you never turn on the corresponding output. Damage to the driving source may happen otherwise.

### 3.3 Application Hints

### 3.3.1 Right Angle Cable

When using right angle M8/M12 connectors, you have to obey the exit direction of the cables when planning the cabling. In figure 6 you find an example with all right angle cables.

figure 6: right angle cable example

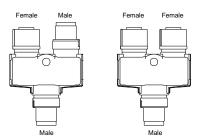

### 3.3.2 M12 Y Adapters

For applications with fieldbus connections that need to pass-through, Y-adapters can be used to provide two sockets for in-coming and out-going cables.

figure 7: M12 Y-connectors

Examples or such adapters are found below:

- M12 5pol A-coded male to female/male: Phoenix Contact SAC-5PY-M/F-M VP SH.

- M12 5pol A-coded male to female/female: Phoenix Contact SAC-5PY-M/2XF VP SH.

# 4 Maintenance

NOTICE

$\bigwedge$

Always follow common ESD practice when you service the product!

All serviceable parts can be reached by removing the top cover of the product.

| Task            | Top<br>Cover | Remarks |

|-----------------|--------------|---------|

| Replace mSATA   | remove       |         |

| Replace Battery | remove       |         |

**NOTICE** All cables should be removed before removing the top cover.

### 4.1 Handling Top Cover

To remove/install the top cover, you need a Torx-T20 tool. A stainless steel tool is preferred.

figure 8: Handling the Top Cover

To remove the top cover, refer to the following instructions:

- Remove the 10 top cover screws as indicated in figure 8

- Lift of the top cover in direction of the screws. Do not apply force in any other direction (rotation, horizontal force), else you might damage the internal high density connector which connects the connectors to the main board.

- Obey that you do not damage the connectors and components on the front panel PCB when you handle the removed top cover.

To install the top cover, refer to the following instructions:

- Check that the sealing is properly installed in its groove

- If IP67 is required, check the integrity of the sealing. If it is damaged, the sealing can be removed and replaced.

- Put the cover onto the housing, gently assigning the high density connector.

- Re-Apply all screws (including the contact washer). Recommended torque: 2.6 Nm.

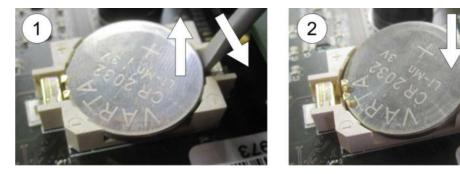

### 4.2 Battery Replacement

### CAUTION

The installed computer board is equipped with a Lithium battery. Danger of explosion if battery is incorrectly replaced. Replace only with battery of the same or equivalent type (3-volt lithium coin cell battery).

- Do not attempt to recharge the battery.

- Do not disassemble, crush, puncture, short external contacts, or dispose of in fire or water.

Compatible battery type: BR2032 (3 Volt lithium coin cell battery)

The battery is used for backing up the system time when the power supply is removed.

- 1. Turn off the computer properly through the operating system, then turn off any external devices.

- 2. Disconnect the power supply from the power connector.

- 3. Remove the top cover from the product and locate the battery on the system main board

- 4. Remove the battery from the holder (See figure 9)

- 5. Insert the new battery (See figure 9)

- 6. Reinstall the top cover

- 1. Removal: Insert screwdriver at right side and bend so that the battery pops outs. Use only gentle force, otherwise the battery holder might be damaged.

- The use a plastic tool is preferred to avoid shorting the battery

- 2. Insertion: Align new battery to the left side of the holder and gently press down on the right side of the battery until the battery snaps into the holder.

figure 9: Removing and replacing coin cell battery

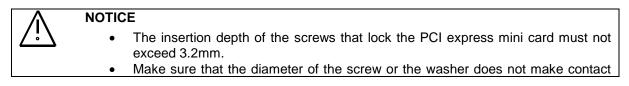

### 4.3 mSATA

After inserting the mini card into the connector, it must be pushed down and locked with two M2,5 screws.

with components or traces on the mini card. Some cards have components very near to the mounting holes.

The mSATA socket only accepts SATA based SSD modules. It does not support PCI express based modules/cards.

# 5 Hardware details

### 5.1 PCI Express

The emPC-CXR uses PCI Express for a couple of expansion options. Some COM Express modules only provide a limited number of PCI Express lanes. Refer to Table 9 for a detailed resource list.

| COM Express<br>PCIe lanes | Function   |

|---------------------------|------------|

| PCIE0                     | Ethernet 2 |

| PCIE1                     | FPGA       |

| PCIE2                     | unused     |

| PCIE3                     | unused     |

| PCIE4                     | unused     |

| PCIE5                     | unused     |

| PCIE6                     | unused     |

| PCIE7                     | unused     |

Table 9: COM Express PCIe lane usage

### 5.2 Ethernet

The emPC-CXR provides two 10/100/1000 ethernet interfaces

#### 5.2.1 LAN1

This Ethernet interface is provides by the COM Express module, refer to the module documentation for details (e.g. controller type).

Wake on LAN implementation depends on the COM Express modules and is usually possible.

#### 5.2.2 LAN2

This Ethernet interface is implanted on the carrier board by an Intel i210 ethernet controller.

The standard configuration uses the i210's iNVM memory for parameter storage. As an option, external FLASH memory option is possible, but not normally equipped on the carrier board.

Wake on LAN is not supported by Ethernet 2.

# 6 FPGA expansion subsystem

The PCIe interface for special Janz Tec Features is implemented by a FPGA and is identified by a set of IDs in PCIe configuration space as listed below:

| Purpose               | Value  | Found in                |

|-----------------------|--------|-------------------------|

| Vendor ID             | 0x13C3 | CFG space register 0x00 |

| Device ID             | 0x2A00 | CFG space register 0x02 |

| Subsystem Vendor ID   | 0x13C3 | CFG space register 0x2C |

| Subsystem ID emPC-CXR | 0x2A00 | CFG space register 0x2E |

Table 10: PCI identification

The FPGA PCIe interface provides access to several register spaces.

| PCI base<br>address<br>register | Description                                   | Size  |

|---------------------------------|-----------------------------------------------|-------|

| 0                               | Local configuration registers (memory mapped) | 512 B |

| 1                               | N/A                                           | -     |

| 2                               | CAN/RS232 address space                       | 8 kB  |

| 3                               | Reserved                                      | 8 kB  |

| 4                               | Control registers                             | 4 kB  |

| 5                               | NVRAM / IO port address space                 | 1 MB  |

Table 11: Local address spaces

The actual addresses for these memory spaces are configured by the BIOS of your system every time the computer is booted. If you wish to access one of these spaces, then you need to read the actual addresses from the PCIe configuration space.

### 6.1 Control Registers

| Address Offset | access | Description    |

|----------------|--------|----------------|

| BAR4 + 0x00    | RO     | INT_STAT       |

| BAR4 + 0x04    | RO     | INT_MASK       |

| BAR4 + 0x08    | WO     | INT_DISABLE    |

| BAR4 + 0x0C    | WO     | INT_ENABLE     |

| BAR4 + 0x10    | WO     | RESET_ASSERT   |

| BAR4 + 0x14    | WO     | RESET_DEASSERT |

| BAR4 + 0x18    | RO     | RESET_STATUS   |

| BAR4 + 0x1c    | RW     | I2C_CONTROL    |

| BAR4 + 0x20    | RO     | FEATURE1       |

| BAR4 + 0x24    | RO     | FEATURE2       |

| BAR4 + 0x30    | RW     | TESTREG        |

| BAR4 + 0x3C    | RO     | REVISON        |

Table 12: Control registers

### 6.1.1 Feature detection

| FI                                                                                   | FEATURE1                                                                                                                                         |      |           |                | BAR4 ·   | + 0x20 (  | 32bit, ro) |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|----------------|----------|-----------|------------|

|                                                                                      | 3110                                                                                                                                             |      | 9         | 8              | 72       | 1         | 0          |

|                                                                                      | reserved                                                                                                                                         |      | COM1      | COM0           | Reserved | CAN1      | CAN0       |

| CAN[10] High if correspon<br>COM[10] High if correspon<br>Reserved Reserved position |                                                                                                                                                  |      | iding CON | /l is availabl | e        | /         |            |

| R                                                                                    | REVISION                                                                                                                                         |      |           |                | BAR4 ·   | + 0x3c (3 | 32bit, ro) |

|                                                                                      | 3124 23                                                                                                                                          |      | 16        | 158            |          | 7         | 0          |

|                                                                                      | ID                                                                                                                                               | Rese | erved     | Rele           | ase      | Bui       | ld         |

| ID<br>Reser                                                                          | Refers to the specific hardware design (0x02 is emPC-CXR)eservedIs 0x00eleaseSpecifies the current Version of the designuildRunning Build Number |      |           |                | २)       |           |            |

#### 6.1.2 Interrupt programming

The FPGA generate an interrupt that is logically or'ed amoung all internal interrupt sources.

To determine which source has generated an interrupt the Interrupt handler must read the interrupt status register:

| INT_STAT |      |      | BAR4 + 0x0 (32bit, ro) |      |      |

|----------|------|------|------------------------|------|------|

| 3110     | 9    | 8    | 72                     | 1    | 0    |

| reserved | COM1 | COM0 | Reserved               | CAN1 | CAN0 |

CAN[1..0] Interrupt status info. Each defined bit in this register reflects the status of the INT# pin of the corresponding CAN. A zero will be read when an interrupt is pending.

|          | If a CAN interrupt request line is disabled, then the corresponding bit is forced to "1".  |

|----------|--------------------------------------------------------------------------------------------|

| COM[10]  | Interrupt status info. Each defined bit in this register reflects the status of            |

|          | the INT# pin of the corresponding COM. A one will be read when an                          |

|          | interrupt is pending.                                                                      |

|          | If a COM interrupt request line is disabled, then the corresponding bit is forced to "0".  |

| Reserved | Reserved positions are undefined, and must not be considered. Software must mask them off. |

Interrupt requests can be masked off by the CPU. This is done through the interrupt disable/enable registers. Interrupts are disabled after RESET, and you need to enable a CAN interrupt line before using it.

| INT_ DISAB      | LE                                                                                                                                                    |                                                           |                                                            | BAR4                                                             | + 0x8 (3                                     | 2bit, wo)                                              |                                      |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------|--------------------------------------|

|                 | 3110                                                                                                                                                  | 9                                                         | 8                                                          | 72                                                               | 1                                            | 0                                                      |                                      |

| re              | eserved                                                                                                                                               | COM1                                                      | COM0                                                       | Reserved                                                         | CAN1                                         | CAN0                                                   |                                      |

| INT_ENABL       | E                                                                                                                                                     |                                                           |                                                            | BAR4 -                                                           | ⊦ 0xC (3                                     | 2bit, wo)                                              |                                      |

|                 | 3110                                                                                                                                                  | 9                                                         | 8                                                          | 72                                                               | 1                                            | 0                                                      |                                      |

| re              | eserved                                                                                                                                               | COM1                                                      | COM0                                                       | Reserved                                                         | CAN1                                         | CAN0                                                   |                                      |

| V[10]<br>VI[10] | Writing one of the<br>function. Both reg<br>a bit disables/end<br>writing zero to a b<br>If a functions in<br>interrupt bit will<br>cause interrupts. | gisters are<br>ables furth<br>bit do not a<br>nterrupt re | e accessed<br>ner interrup<br>affect the ir<br>equest line | in hot-1 tech<br>ots from the o<br>nterrupt mask<br>e is disable | inique: V<br>correspo<br>status c<br>d, then | Vriting a o<br>nding fund<br>of that fund<br>this fund | one to<br>ction,<br>ction.<br>ctions |

Reserved bit positions must be written as zero.

#### 6.1.3 Function Reset

To ensure a defined state of a function at any time, it is possible to activate the RST# line of a function via software. This can be done with the reset assert/deassert registers. The RST# line of all functions are activated during a PCIe bus reset.

| RESET_A                        | SSERT                                                                                                                                                                  |                                                                    |                                                                           | BAR4 +                                                                   | • 0x10 (3                                       | 2bit, wo)                                                |                                    |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------|------------------------------------|

|                                | 3110                                                                                                                                                                   | 9                                                                  | 8                                                                         | 72                                                                       | 1                                               | 0                                                        |                                    |

|                                | reserved                                                                                                                                                               | COM1                                                               | COM0                                                                      | Reserved                                                                 | CAN1                                            | CAN0                                                     |                                    |

| RESET_D                        | EASSERT                                                                                                                                                                |                                                                    |                                                                           | BAR4 +                                                                   | • 0x14 (3                                       | 2bit, wo)                                                |                                    |

|                                | 3110                                                                                                                                                                   | 9                                                                  | 8                                                                         | 72                                                                       | 1                                               | 0                                                        |                                    |

|                                | reserved                                                                                                                                                               | COM1                                                               | COM0                                                                      | Reserved                                                                 | CAN1                                            | CAN0                                                     |                                    |

| CAN[10]<br>COM[10]<br>Reserved | Writing one of the<br>function. Both re-<br>a bit disables/en<br>writing zero to a<br>If a functions in<br>interrupt bit will<br>cause interrupts.<br>Reserved bit pos | gisters are<br>ables furth<br>bit do not<br>nterrupt r<br>never ap | e accessed<br>her interrup<br>affect the in<br>equest line<br>pear in the | in hot-1 tech<br>ots from the<br>nterrupt mask<br>is disable<br>INT_STAT | nnique: V<br>correspo<br>k status c<br>ed, then | Vriting a or<br>nding func<br>of that func<br>this funct | ne to<br>ction,<br>ction.<br>tions |

### 6.1.4 Internal I<sup>2</sup>C bus

The control register for the onboard I<sup>2</sup>C interface provides bit-bang style I2C implementation.

| I2C_C    | CONTROL                        |                                                                             |                         | BAR4         | BAR4 + 0x1c (32bit, rw) |     |   |

|----------|--------------------------------|-----------------------------------------------------------------------------|-------------------------|--------------|-------------------------|-----|---|

|          | 3110                           | 9                                                                           | 8                       | 72           | 1                       | 0   |   |

|          |                                | reserved                                                                    |                         |              | SCL                     | SDA |   |

| SDA      | Writing 0 set<br>Writing 1 tri | onal data line.<br>ts the data line<br>istates the dat<br>ne to high poter  | ta line. Ar             | n external p | •                       | •   | , |

| SCL      | Writing 0 set<br>Writing 1 tri | onal" clock line<br>ts the clock line<br>istates the clo<br>ne to high pote | to low po<br>ck line. A | n external p |                         |     |   |

| Reserved | Reserved bit                   | t positions mus                                                             | t be writte             | n as zero.   |                         |     |   |

### 6.2 CAN Interface

### 6.2.1 CAN address space

The CAN controllers are mapped into memory address space

| Address Offset    | accesses:                            |

|-------------------|--------------------------------------|

| BAR2 + 0x0000x0ff | CAN controller 0 registers (SJA1000) |

| BAR2 + 0x1000x102 | CAN controller 0 control             |

| BAR2 + 0x2000x2ff | CAN controller 1 registers (SJA1000) |

| BAR2 + 0x3000x302 | CAN controller 1 control             |

Refer to SJA1000 manual for description of registers and operation.

### 6.2.2 CAN termination and LEDs

Besides the registers of the SJA1000 (which are defined in the SJA1000 Manual), there are two additional registers which control the line termination and the front panel LEDs. These registers are unique for each channel.

| CAN_   | TERM | 0,1 | BAR     | 2 + 0x | 100, O | x300 (l | oyte, rw) |

|--------|------|-----|---------|--------|--------|---------|-----------|

| 7      | 6    | 5   | 4       | 3      | 2      | 1       | 0         |

|        |      |     | reserve | ed     |        |         | TERM      |

| RESET: |      |     |         |        |        |         |           |

|        |      |     | -       |        |        |         | 0         |

TERM Set to zero to disable the line-termination, Set to one to enable the termination resistor.

Reserved

Reserved positions should not be changed. You should use read-modifywrite operation to change this register.

| CAN_I  | LED0, <sup>-</sup> | 1    | BAR   | 2 + 0x | 102, 0 | x302 (by | /te, wo) |

|--------|--------------------|------|-------|--------|--------|----------|----------|

| 7      | 6                  | 5    | 4     | 3      | 2      | 1        | 0        |

|        |                    | rese | erved |        |        | LEDG     | LEDR     |

| RESET: |                    |      |       |        |        |          |          |

|        |                    |      | -     |        |        | 0        | 0        |

| LEDR     | Write 1 to turn red LED on, write 0 to disable.                                      |

|----------|--------------------------------------------------------------------------------------|

| LEDG     | Write 1 to turn green LED on, write 0 to disable.                                    |

| Reserved | Reserved positions should be written as zero for compatibility with future products. |

| RESET: |   |   |   |   |   |   |   |

|--------|---|---|---|---|---|---|---|

| -      | 0 | - | 1 | 1 | 1 | - | 0 |

### 6.3 Serial Port Interface

#### 6.3.1 Serial Port address space

The UART controllers are mapped into memory address space

| Address Offset      | accesses: |

|---------------------|-----------|

| BAR2 + 0x10000x1008 | UART 0    |

| BAR2 + 0x11000x1108 | UART 1    |

The serial port UARTs are implemented inside the FPGA and are 16550 compatible (16 bytes FIFO).

. . . . . . . . . . . . . . . .

- On customer request other serial port options are possible, but *not yet* implemented:

The COM Express Typ 6 defined serial ports (Rx/TX only) can be routed to the connectors. Implementation depends on availability on the COM Express module. Sometimes such ports are available as legacy ports, sometimes as USB based ports, sometimes as custom ports, sometimes they are not available at all.

- LPC based legacy serial ports (IO address) can be implemented in FPGA if legacy ports are required for software compatibility. BIOS support for such ports can be a difficult issue however.

### 6.4 NVRAM

The emPC-CXR implements an integrated nvSRAM memory. This device implements 128kx8 NVRAM. The NVRAM is a fast SRAM style device, however there is no need for battery maintenance.

| Address                 | Description |

|-------------------------|-------------|

| BAR5 + 0x0800000x09FFFF | NVRAM area  |

Table 13: NVRAM address (128KByte NVRAM)

The NVRAM can be accessed by 8-, 16- and 32 bit operations (read and write).

If NVRAM is accessed by 16/32 bit operations, these are not atomic. In case of power down, it might happen that only parts of the 16/32 bit value are stored in the nvSRAM. Also notice that the PCI interface has buffers. Even if the write operation has been finished from CPU point of view, it might not have been saved into the memory. To make sure data has reached the memory, you need to read back the latest written content.

### 6.5 Digital IO

Programming the digital IO is utilized by reading/writing register in the FPGA register space.

| Address Offset | access | Description |

|----------------|--------|-------------|

| BAR5 + 0x00    | -      | -           |

| BAR5 + 0x01    | RW     | DIGIO_OUT   |

| BAR5 + 0x02    | WO     | DIGIO_IN    |

| BAR5 + 0x03    | RO     | DIGIO_STAT  |

Table 14: Digital IO registers

|       | DIGIO                                                                             | _OUT    |          |      | BA                  | R5+0x′            | 1 (byte         | e, rw)            |

|-------|-----------------------------------------------------------------------------------|---------|----------|------|---------------------|-------------------|-----------------|-------------------|

|       | 7                                                                                 | 6       | 5        | 4    | 3                   | 2                 | 1               | 0                 |

|       | write                                                                             | 0, read | as don't | care | OUT3                | OUT2              | OUT1            | OUT0              |

|       | DIGIO                                                                             | _IN     |          |      | BAR5+0x2 (byte, ro) |                   |                 |                   |

|       | 7                                                                                 | 6       | 5        | 4    | 3                   | 2                 | 1               | 0                 |

|       | IN3                                                                               | IN2     | IN1      | IN0  | r                   | ead as o          | don't car       | e                 |

| IN30  | status of the digital input line<br>0: input voltage 04V<br>1: input voltage 924V |         |          |      |                     |                   |                 |                   |

| OUT30 |                                                                                   |         |          |      |                     |                   |                 |                   |

| 00130 | 1: input v                                                                        |         | 924∨     |      | ВА                  | R5+0x             | 3 (byt          | e, ro)            |

| 00130 | 1: input v                                                                        | oltage  | 924∨     |      | <b>BA</b><br>3      | <b>R5+0x</b><br>2 | <b>3 (byt</b> e | e, ro)<br>0<br>NO |

NO

1: Normal operation.

0: Overheat condition; the output port is shutting down. This may result in cooling down the chip which sets the NO flag back to 1. If the error still exists, the chip will heat up again and the NO flag will be set to 0.

# 6.6 **FPGA** Reprogramming

An interface is provided to reprogram the SPI Flash of the FPGA.

| SPI_RX                                      | < colored and set of the set of t |                                                                   | 310                                                            | BAR         | 0 + 0x100 (  | 32bit, ro)                    |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------|-------------|--------------|-------------------------------|

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                 | X_DATA                                                         |             |              |                               |

| RX_DATA                                     | Data read f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | rom SPI FLA                                                       | SH. Data is s                                                  | hifted in a | t LSB.       |                               |

| SPI_TX                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   | 310                                                            | BAR         | 0 + 0x104 (3 | 32bit, rw)                    |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Т                                                                 | X_DATA                                                         |             |              |                               |

| TX_DATA                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   | PI FLASH. [<br>r is enabled (                                  |             |              | hen SPI_TX is<br>d out first. |

| SPI_CC                                      | ONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                   |                                                                | BAR         | ) + 0x108 (3 | 32bit, rw)                    |

| 3125                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1914                                                              | 14 13                                                          | 12          | 111          | 0                             |

| Reserve                                     | ed SHIFT F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   | VP HOLD                                                        | CS          | Reserved     | EN                            |

| RESET:                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                 | 1 1                                                            | 1           | I _          | 0                             |

| EN<br>CS<br>HOLD<br>WP<br>SHIFT<br>Reserved | SPI FLASH<br>SPI FLASH<br>SPI FLASH<br>Data shift c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HOLD# cont<br>WP# control<br>ount. N+1 bit<br>positions are       | control (0=low<br>trol (0=low)<br>I (0=low)<br>s are shifted o | out when    | _            | vritten.<br>nsidered. Write   |